PETsys Front-End Type D Module

Core component of the PETsys SiPM readout system

The PETsys FEB/D modules serve as the central interface between front-end modules (FEMs) and the DAQ system, collecting event records from TOFPET ASICs and transmitting them to the data acquisition computer. FEB/D modules also provide power, configuration, clock, and synchronization signals to the ASICs, as well as adjustable bias voltages to the SiPM arrays. Integrated with the Clock & Trigger module, they enable system-wide coincidence detection and veto of non-coincident events in firmware.

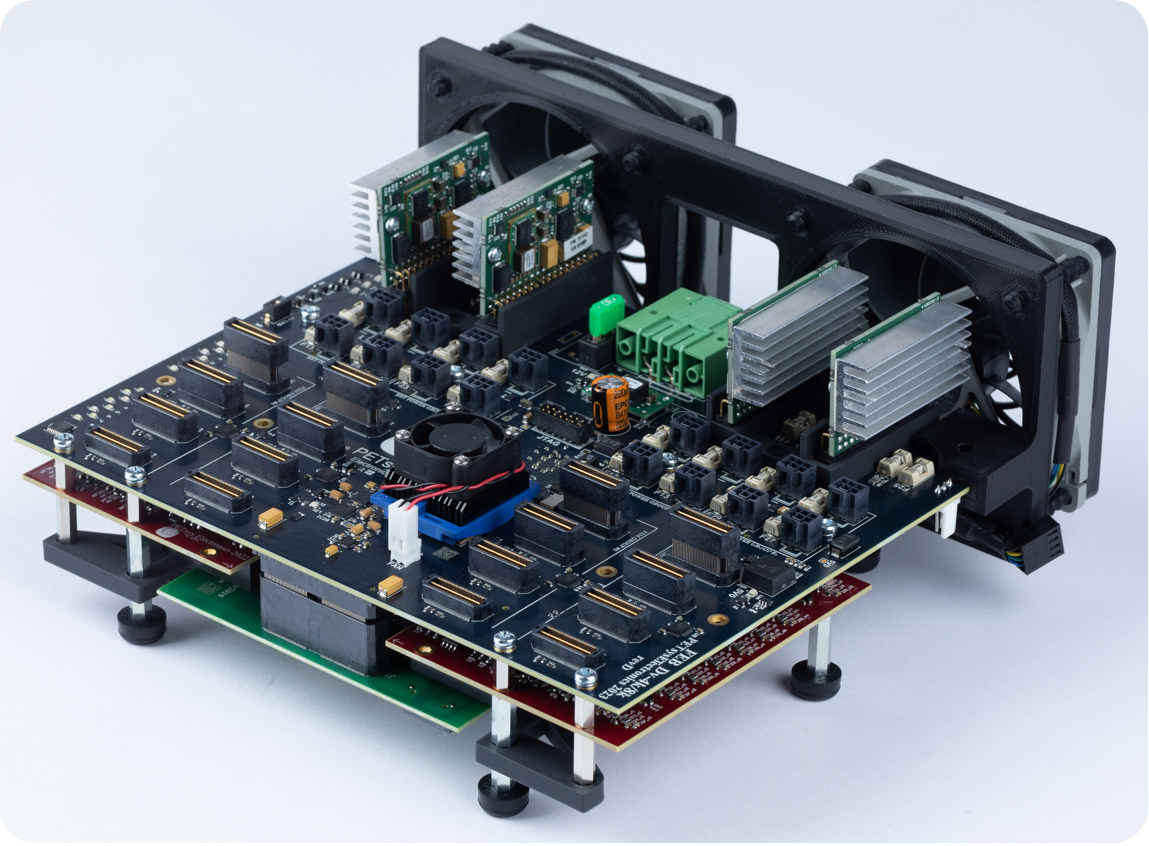

Two versions of the FEB/D module are available: the FEB/D-1k, optimized for small to medium-sized systems with a moderate number of channels, and the FEB/D-8k, built for large-scale PET systems requiring high scalability.

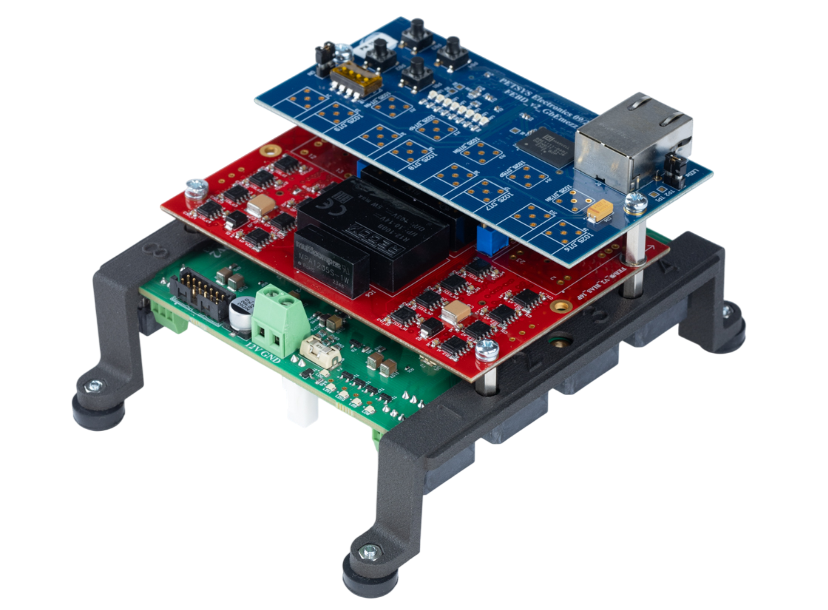

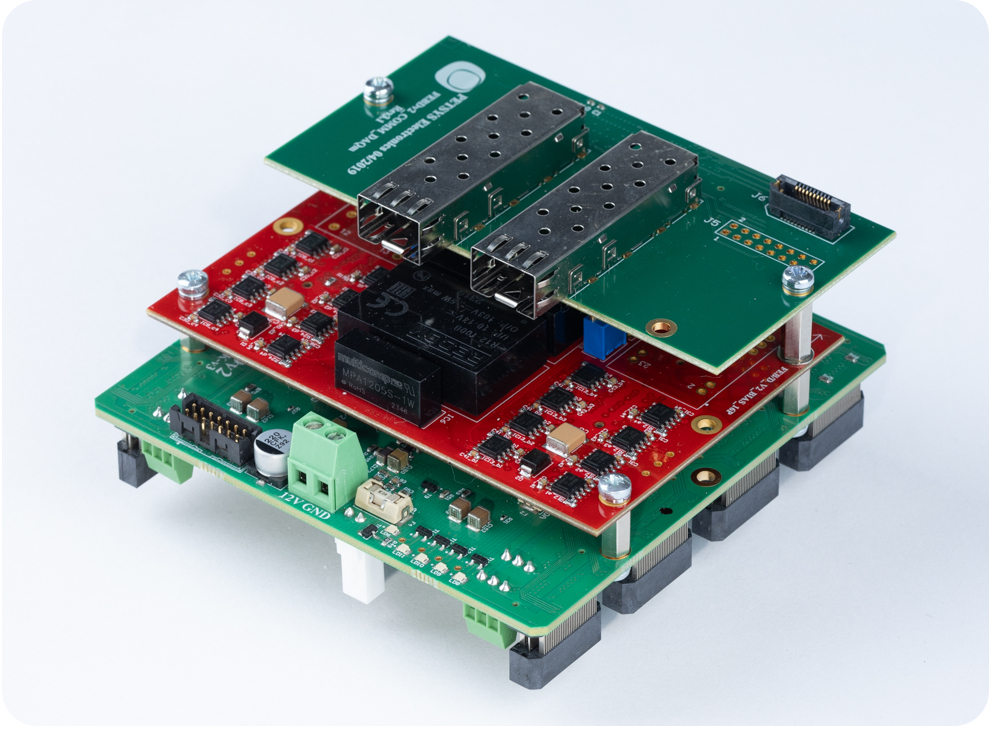

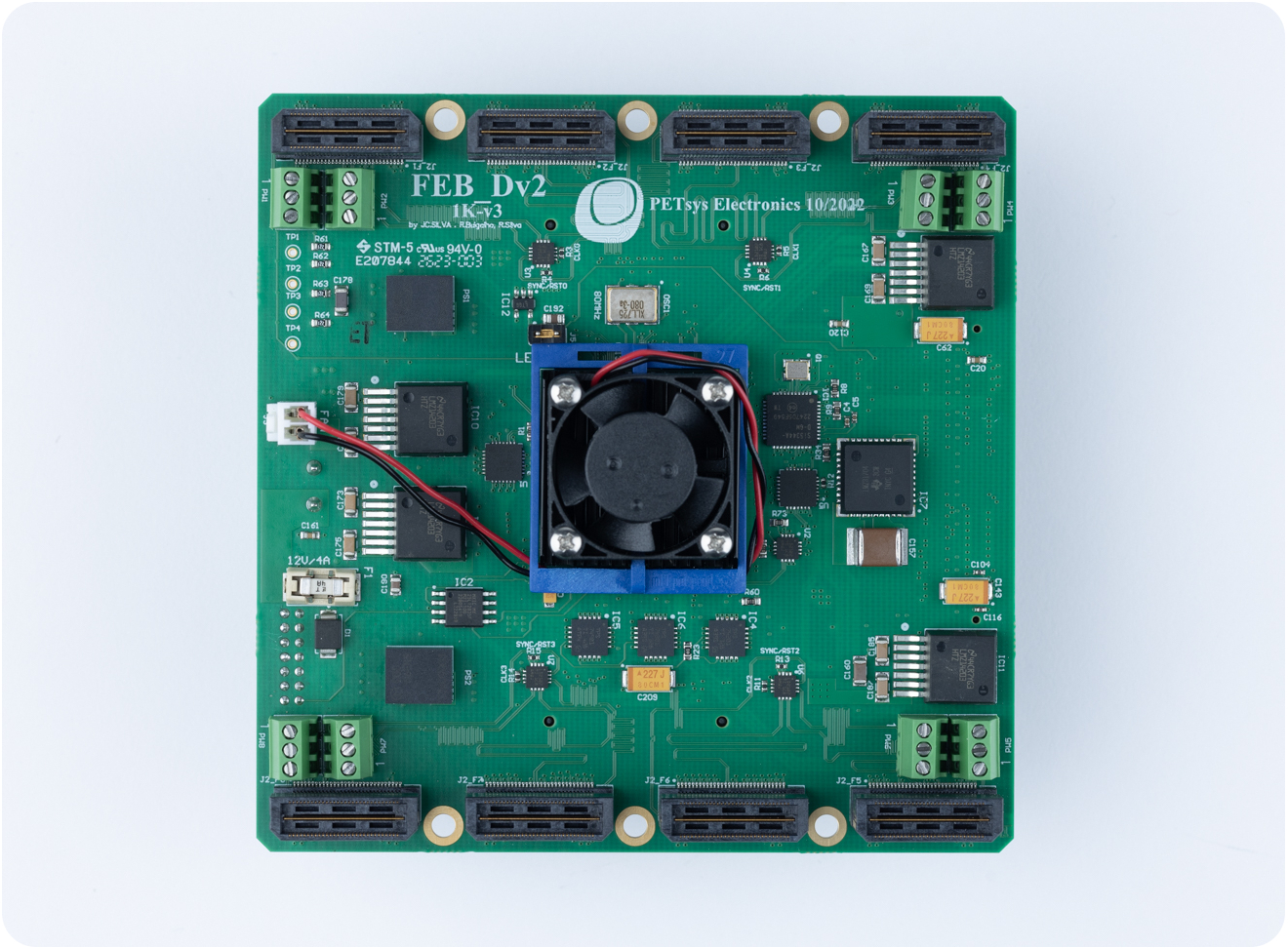

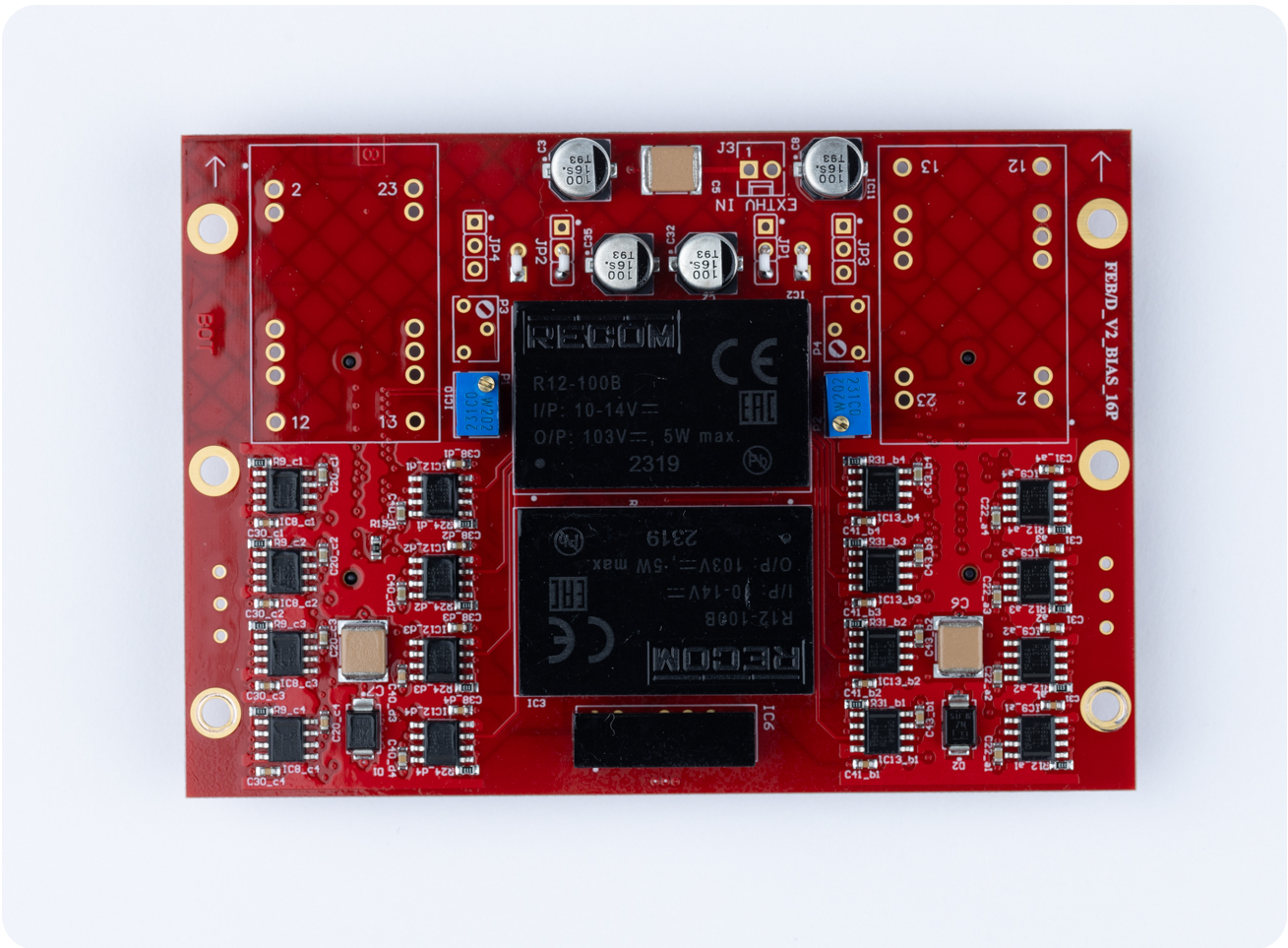

The FEB/D-1k features a compact 104.5x104.5 mm motherboard equipped with a Kintex-7 FPGA. It connects to eight FEM128 or four FEM256 modules via direct board-to-board connectors or flexible coaxial cables. The module includes a communication mezzanine with SFP+ ports operating at 6.6 Gbit/s, enabling maximum event output rates of 100 Mcps and daisy-chain capability for up to 32 modules. A Gigabit Ethernet option is available for smaller systems with 15 Mevents/s output. The bias voltage mezzanine provides 16 positive bias lines (0-72V, 2.5mA per line). Operating on 12 Vdc with maximum 4A draw, the module features onboard DC-DC converters and a 200 MHz clock frequency.

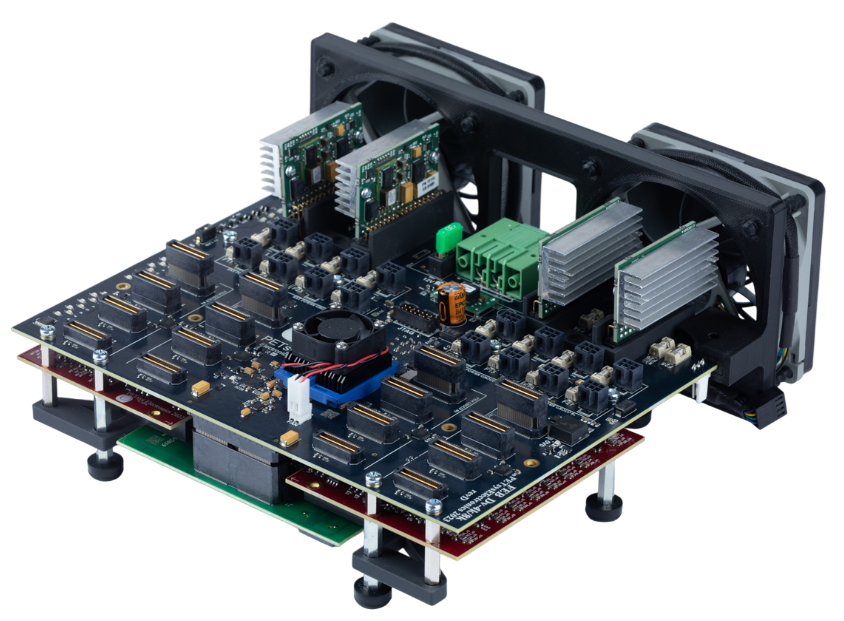

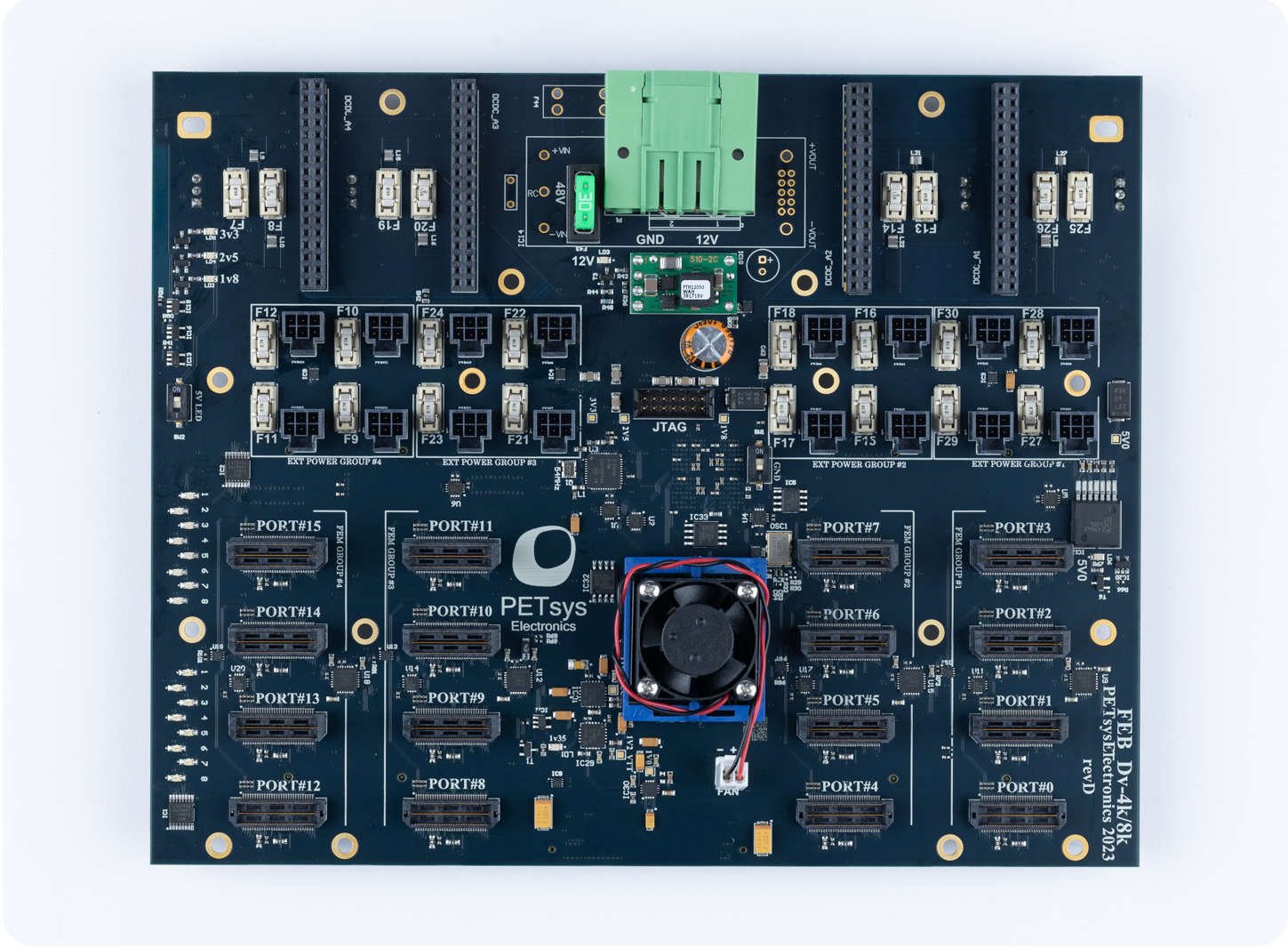

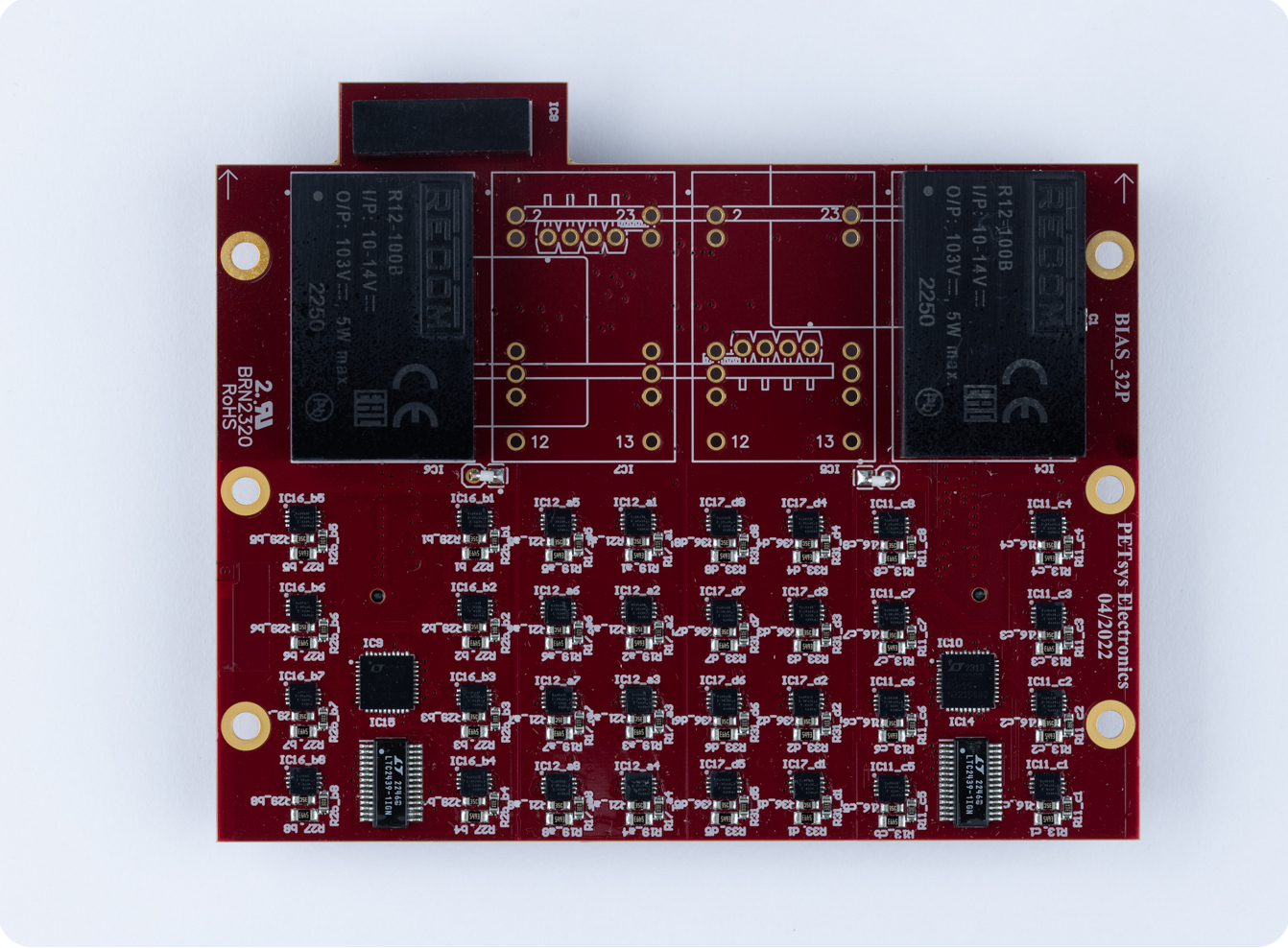

Designed for larger systems, the FEB/D-8k handles up to 8,192 channels from 16 front-end modules (FEM128, FEM256, or FEM512). The 208x166.3 mm motherboard houses both Kintex-7 and Spartan-7 FPGAs with pre-installed firmware. Two bias voltage mezzanines provide 32 configurable bias lines (0-60V, 2mA per line). Like the FEB/D-1k, it supports daisy-chaining of up to 32 modules, 100 M events/s output rate, and operates on 12 Vdc (maximum 25A). Both modules receive synchronization from the Clock&Trigger module and can accept veto signals for optimized event filtering.

FEB/D-1K

FEB/D-8K

FEB/D-8K motherboard featuring 16 connectors for front-end modules and a central Kintex-7 FPGA. Additional power connectors are also available to compensate for voltage drops when using long cables to FEMs.

Main Features

- Based on PETsys TOFPET2 ASIC and compatible with PETsys FEB/D and DAQ-PCiE boards for seamless system integration.

- Equipped with Kintex-7 FPGA with pre-installed firmware that can be easily upgraded for new features and improvements.

- Compatible with FEM128 and FEM256 front-end modules (and also FEM512 upon request) for flexible detector array configurations

- Multiple data output options available: SFP+ optical/copper links or Gigabit Ethernet mezzanines for versatile connectivity solutions

- Maximum event output rate of 100 M events/s through high-speed SFP+ links operating at 6.6 Gbit/s bandwidth

- Daisy-chain capability allows up to 32 FEB/D modules to connect to a single DAQ board.

- Receives 200 MHz clock and synchronization signals from Clock&Trigger module through LVDS interface at 400 Mbit/s.

- Onboard DC-DC converters provide regulated power to ASICs in connected front-end modules from 12 Vdc supply.

- Integrated bias voltage mezzanines supply adjustable voltages (0-72V) to SiPM arrays with configurable current options per line.

- Firmware coincidence filtering and veto signal capability from Clock&Trigger module optimizes data rate transmission.