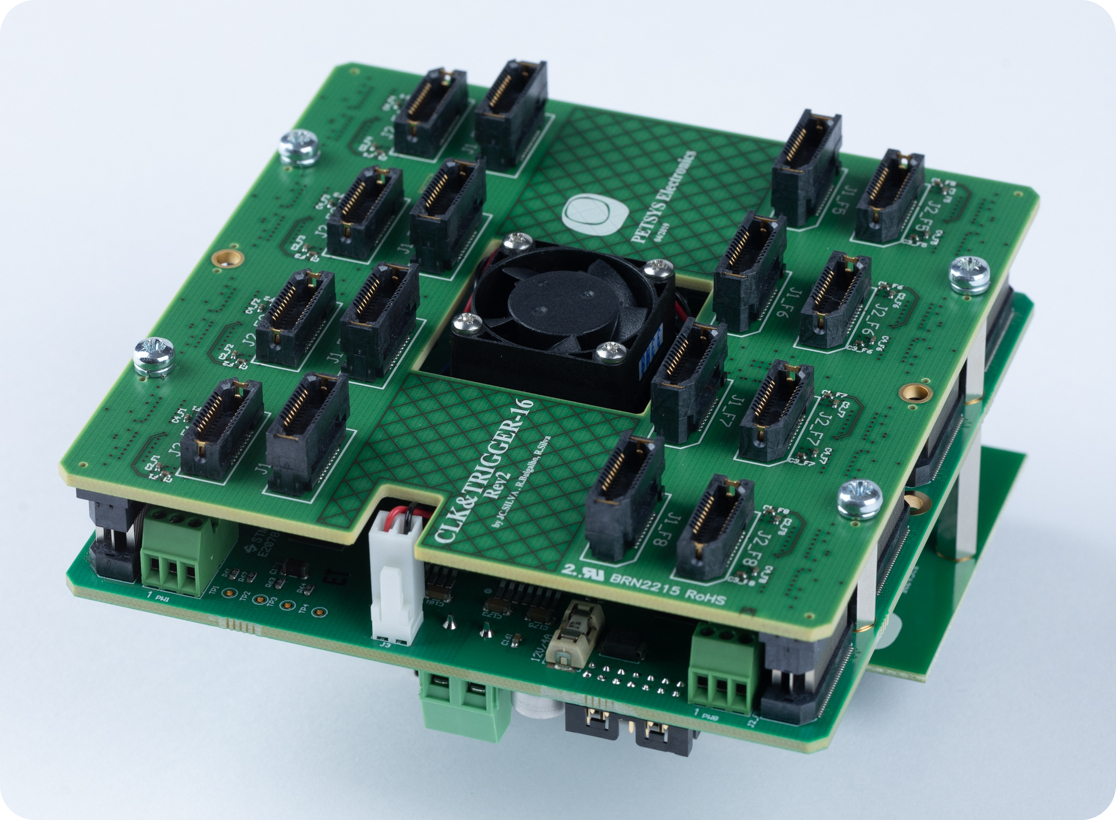

PETsys Clock & Trigger Module

Core component of the PETsys SiPM readout system

The PETsys Clock & Trigger (CLK&TGR) module serves as the central timing and synchronization hub for PETsys SIPM Readout systems. Connected to all FEB/D modules via Samtec ERCD flat coaxial cables, it distributes precise 200 MHz clock signals and synchronization commands throughout the entire system.

The module implements sophisticated system-wide coincidence filtering through advanced firmware running on a Kintex-7 FPGA. It continuously collects coarse time information from all connected FEB/D modules and analyzes time and system correlations in real-time to determine which events form valid coincidences. Events that do not meet the coincidence criteria are discarded, reducing the data bandwidth required between the front-end electronics and the DAQ computer. This FPGA-based firmware filtering approach significantly improves overall system efficiency, reduces processing load on the DAQ system, and enables higher sustainable event rates across the detector array.

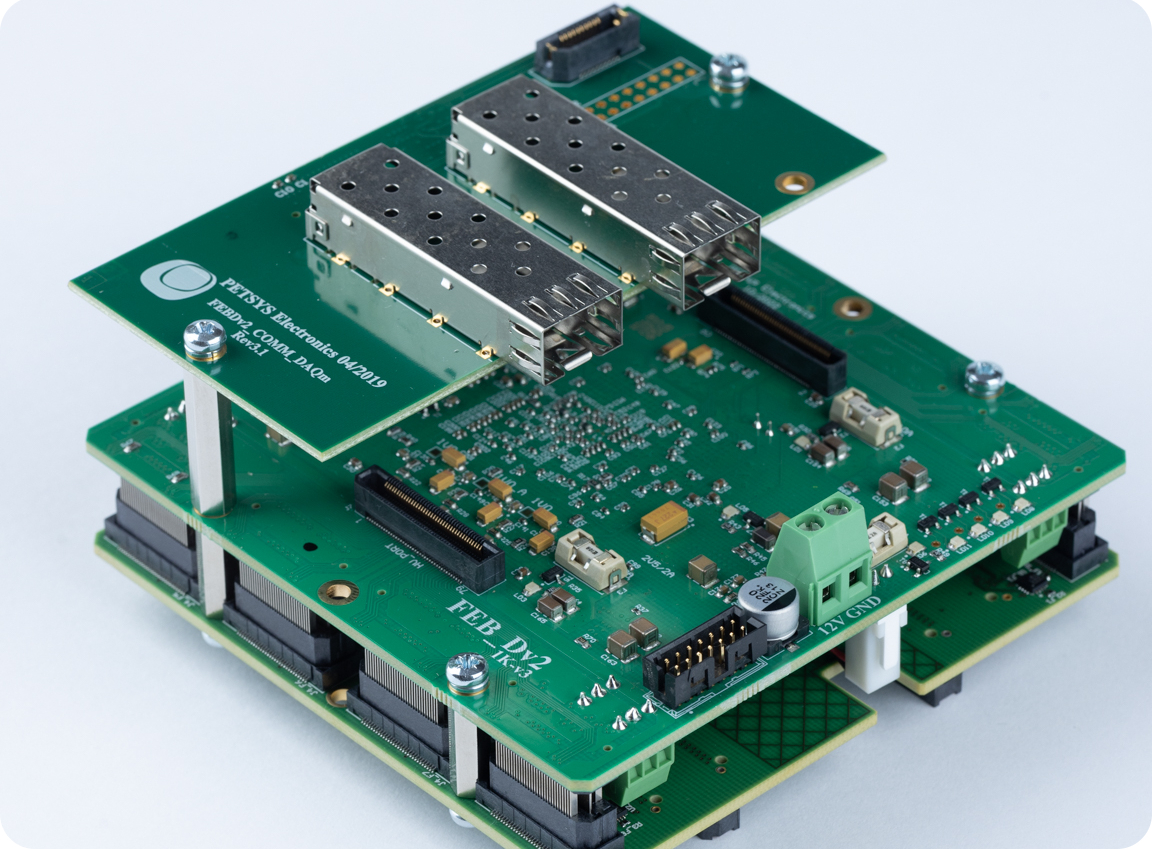

Built on the same motherboard as FEB/D modules, it shares the communication mezzanine and protocol, allowing seamless daisy-chain integration with other FEB/Ds and the DAQ board. The standard module supports up to 16 FEB/D modules with 4 trigger regions each, with larger configurations available upon request.

For multi-system integration, it can accept or provide external clock and synchronization signals, and supports veto signals that globally disable event recording across all connected modules.

Main Features

- Distributes 200 MHz clock and synchronization signals to all FEB/D modules via Samtec ERCD flat coaxial cables for precise system-wide timing

- Implements real-time coincidence filtering using Kintex-7 FPGA firmware, discarding non-coincident events at hardware level to reduce DAQ bandwidth

- Supports up to 16 FEB/D modules with 4 trigger regions each; larger configurations available upon request for scalable system designs

- Accepts or provides external clock and synchronization signals for multi-system integration; supports veto signals for global event recording control