PETsys SiPM

Readout System

The PETsys SiPM Readout System is engineered for reading large numbers of SiPM photosensor pixels in applications requiring high data rates and excellent time resolution. Built around the low-power TOFPET2 ASIC, the system provides a complete and scalable data acquisition solution capable of managing tens of thousands of independent SiPM channels.

The system comprises four main component types that work together seamlessly:

- Front-End Modules (FEMs) interface directly with SiPM arrays, converting analog photosensor signals to digital data. Available in configurations reading 128, 256, or 512 channels, FEMs are optimized for different system scales and geometries. The modules feature low power consumption (14 mW/channel) and support maximum event rates from 300-500 kcps per channel depending on configuration.

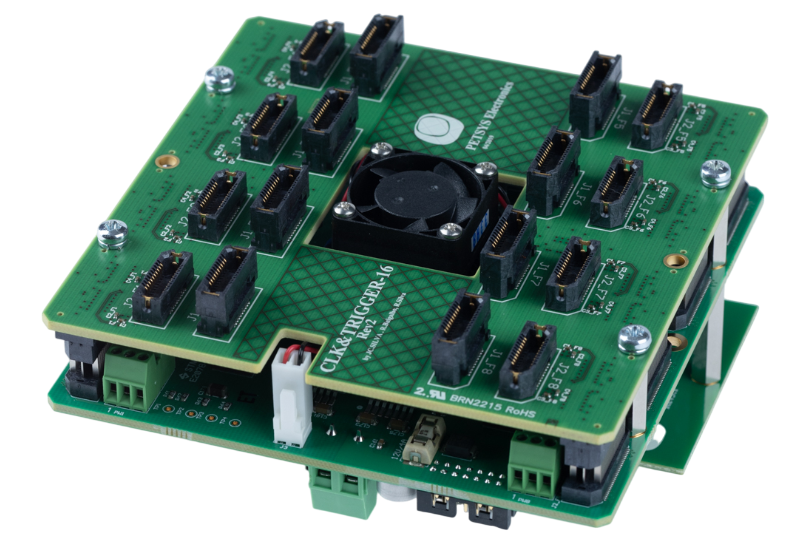

- Clock & Trigger Boards distribute system-wide timing, synchronization, and coincidence triggers to up to 16 or 64 FEB/D boards, ensuring coherent operation across the entire system.

- Front-End Type D Boards (FEB/D) aggregate and process data from multiple FEMs. The FEB/D-1k handles up to 1,024 channels from eight FEM128 modules, while the FEB/D-8k manages up to 8,192 channels from sixteen FEMs. These boards provide power, configuration signals, clock synchronization, and adjustable SiPM bias voltages. They implement sophisticated coincidence filtering and energy triggers in firmware, significantly reducing data transmission while preserving critical events.

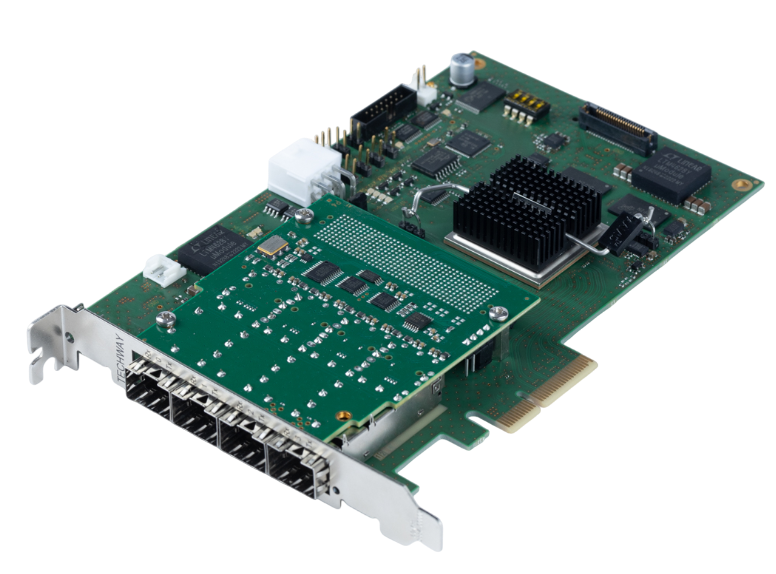

- DAQ-PCIe Cards provide high-speed computer interface with throughput up to 230 Mevents/s per card. Up to two cards can be installed per DAQ computer.

This modular design enables configurations from small systems (256 channels with a single FEB/D and Ethernet connection, requiring no additional DAQ or Clock & Trigger boards) to large-scale installations exceeding 100,000 channels using multiple daisy-chained FEB/D modules. Up to 32 FEB/D boards can be connected in a single chain, with systems expandable to 196,608 channels and beyond using multiple DAQ modules.

The system includes comprehensive firmware and software running under Linux, featuring an intuitive graphical user interface for easy operation. Intelligent firmware implements energy and coincidence triggers with configurable time windows, typically reducing data rates by a factor of 10 while maintaining all relevant events. The system supports synchronization with external equipment and offers flexible trigger configurations, making it adaptable to diverse detector geometries and application requirements beyond traditional PET imaging.

Contact us to discuss your specific system architecture and receive a customized quote.

PETsys Front-End Modules

PETsys Front-End ModulesThe PETsys Front-End modules are the interface between the analog signals of the photo-sensor and the digital readout chain.

PETsys Front-End Type D Modules

The PETsys Front-End module is the interface between the analog signals of the photo-sensor and the digital readout chai

Clock&Trigger Module

Clock&Trigger ModuleBottom view showing the connectors for the 16, 3M 3896 series cables providing clock and trigger signals to the FEB/D Modules.

DAQ Board

DAQ Board The DAQ board plugs into the PCIe bus of the DAQ computer.

Main Features

- Modular architecture scales from 256 to over 100,000 SiPM channels with identical core components

- Low power consumption: 14 mW per channel including ASIC, buffers, and voltage regulators

- High event rates: 300-500 kcps per channel depending on Front-End Module configuration

- Intelligent coincidence filtering in firmware reduces data rates by a significant factor

- Flexible connectivity: Ethernet for small systems, optical/copper SFP+ links for larger installations

- Complete software suite with GUI and open-source code (Python/C++) under MIT license

- Independent bias voltage control with up to 64 adjustable channels per FEB/D board

- Daisy-chain topology allows up to 32 FEB/D modules per single DAQ input